Intel announced new technologies for its next chips at IEDM 2024. Emphasis is a new method of execution Interconnects in semiconductors using subtractive ruthenium and ultra-thin wafer solutions.

Extractive ruthenium is found in platinum mines and is used to strengthen metal alloys. The company says so It will use air gaps and high resistance to reduce line-by-line electricity storage capacity in chips by up to 25%.

Adopting ruthenium is also a way to replace the damask copper currently used in connections between silicon. The new method does not require more expensive lithographs and is a process that is “integrated, practical, economical and compatible with large-scale production,” according to the company.

Ultra-thin wafers

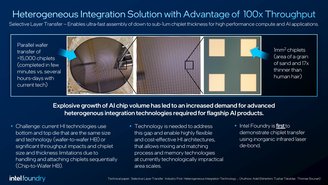

The event also revealed advances in the massive production of silicon wafers used by Intel’s manufacturing division. The new feature is Selective Layer Transfer (SLT), i.e. Technology that allows the development of ultra-thin sheets, leading to increasingly smaller chips.

The idea of the new procedure is that these packages greater functional intensity and more flexible useWafers are known to be extremely fragile. Therefore, the company’s expectation is that the chip-to-chip transfer speed will be up to 100 times faster.

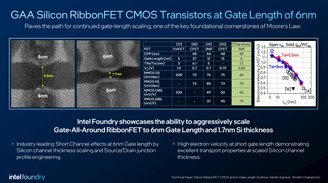

Developments in RibbonFET GAA

During the presentation, Intel Foundry highlighted innovations in GAA (gate all around) transistors. An example of this is new 6-nanometer CMOS (Complementary Metal Oxide Semiconductor) RibbonFET transistors onlyTo achieve this size, there were significant reductions in the size of the channels.

It is also worth remembering that RibbonFET technologies will be used directly in the 18A production process at 1.8 nm. To complement this type of technology, the company also announced NMOS and PMOS transistors with 2D GAA using transition metal dichalcogenide as a possible alternative to silicon in advanced processing in this category.

For now, these transistors are only in the research phase and it will take some time before they are included in the company’s products. In addition to the announcements at IEDM 2024, Intel is expected to appear at CES 2025 in January with new products for the domestic market.

Source: Tec Mundo

I am a passionate and hardworking journalist with an eye for detail. I specialize in the field of news reporting, and have been writing for Gadget Onus, a renowned online news site, since 2019. As the author of their Hot News section, I’m proud to be at the forefront of today’s headlines and current affairs.